DS92CK16

Description

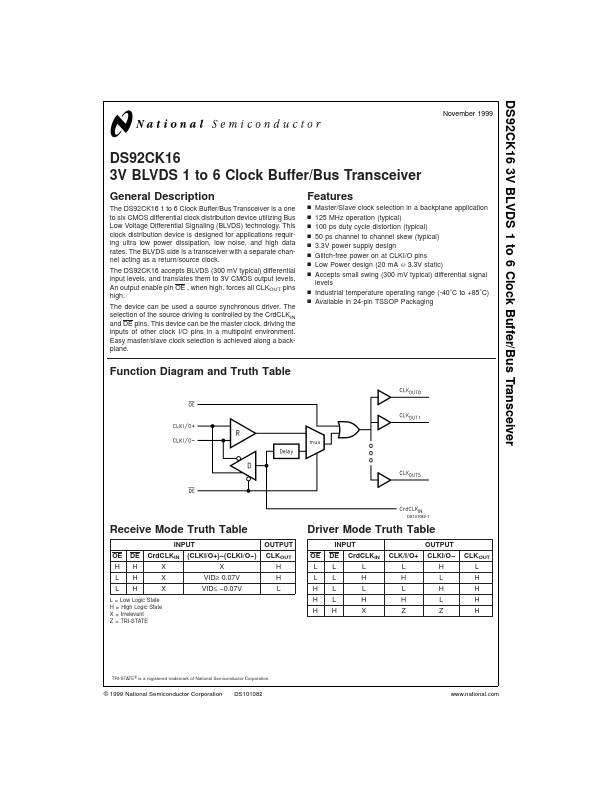

The DS92CK16 1 to 6 Clock Buffer/Bus Transceiver is a one to six CMOS differential clock distribution device utilizing Bus Low Voltage Differential Signaling (BLVDS) technology.

Key Features

- Industrial temperature operating range (-40˚C to +85˚C)

- Available in 24-pin TSSOP Packaging n n n n n n n

- OUTPUT CLKI/O- H L H L